|

|

|

|

ELE301/302:

Digital Design with FPGAs

|

Catalog Descriptions:

ELE 301 Digital Design with FPGAs (3)

Digital design, simulation, synthesis and verification using

electronic design automation (EDA) tools.

IEEE VHDL hardware description language and rapid prototyping with FPGAs.

Register transfer level design with reusable modules and cores.

(Lec. 3, Lab. 3) Pre: 201, 202, 212 and 215, and credit or concurrent enrollment in 302.

ELE302 Digital Design with FPGAs Lab. (1)

Laboratory exercises related to topics in 301.

Pre: 201, 202, 212, and 215, and credit or concurrent enrollment in 301.

|

|

|

|

The main software tool for this class is the

Altera’s Quartus II.

This is a comprehensive package which includes schematic editor, state diagram editor,

VHDL and Verilog entry and synthesis tools, integrated waveform and timing

simulator, DSP design tools and utilities, and FPGA implementation and

configuration tools. Altera offers a free "web edition" of Quartus II; which

can be downloaded directly from the company website. Students are

encouraged to obtain this free program to use at home.

|

|

|

|

|

|

|

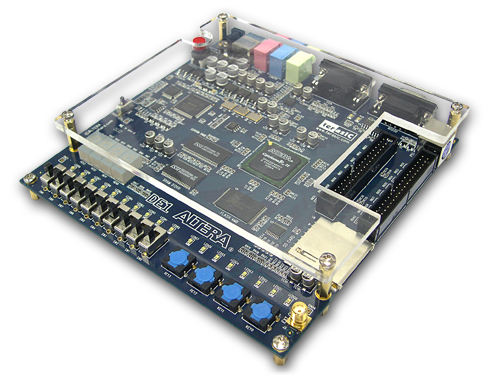

The main hardware facility is the

Terasic’s

DE1-SoC board from Altera's University Program. It carries an

Altera's Cyclone V SE 5CSEMA5F31C6N FPGA. This FPGA has 32,070

programmable Adaptive logic module (ALMs), about 4M bits of on-chip memory, 87 embedded 9-bit

multipliers, and four phase locked loops (PLLs).

The FPGA has a hard processor system consists of a 800MHz dual-core ARM Cortex-A9 processor with 1GB DDR3 SRAM, Ethernet, two USB ports and a Micro SD card socket.

The FPGA configuration file is downloaded from

the host computer via USB port.

|

|

|

|

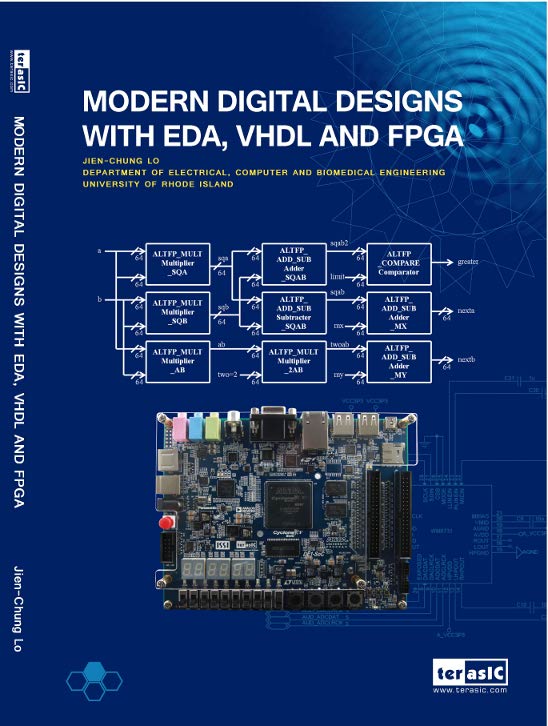

Textbook:

J. C. Lo, Modern Digital Designs with EDA, VHDL and FPGA.

Published by

Terasic, 2015.

|

|

|

Spring 2018 schedule:

301 Lecture: MWF 11:00 -- 11:50 AM @ Pastore 234

302 Lab 01: Tu 2:15 -- 5:00 PM @ Schneider 200J

302 Lab 02: We 2:15 -- 5:00 PM @ Schneider 200J

302 Lab 03: Th 2:15 -- 5:00 PM @ Schneider 200J

302 Lab 04: Mo 2:15 -- 5:00 PM @ Schneider 200J

|

|