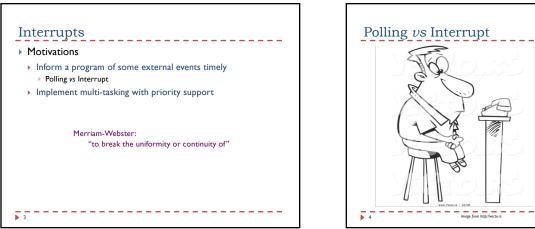

## Polling: You pick up the phone every three seconds to check whether you are getting a call. Interrupt: Do whatever you should do and pick up the phone when it rings.

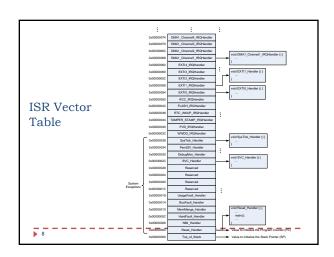

| <ul> <li>Start address for the<br/>exception hander for<br/>each exception type is<br/>fixed and pre-defined</li> <li>Processor loads PC</li> </ul> | Address                         | Priority | Type of  | Acronym            | Description                                                                                    |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------|----------|--------------------|------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                     |                                 |          | priority | Action             |                                                                                                |  |  |

|                                                                                                                                                     | 0x0000_0000                     | -        | •        | -                  | Stack Pointer                                                                                  |  |  |

|                                                                                                                                                     | 0x0000_0004                     | -3       | fixed    | Reset              | Reset Vector                                                                                   |  |  |

|                                                                                                                                                     | 0×0000_0008                     | -2       | fixed    | NMI_Handler        | Non maskable interrupt. The RCC<br>Clock Security System (CSS) is<br>linked to the NMI vector. |  |  |

|                                                                                                                                                     | 0x0000_000C                     | -1       | fixed    | HardFault_Handler  | All class of fault                                                                             |  |  |

| with this fixed, pre-                                                                                                                               | 0x0000_0010                     | 0        | settable | MemManage_Handler  | Memory management                                                                              |  |  |

| defined address                                                                                                                                     | 0x0000_0014                     | 1        | settable | BusFault_Handler   | Pre-fetch fault, memory access fault                                                           |  |  |

| Exception Vector Table                                                                                                                              | 0x0000_0018                     | 2        | settable | UsageFault_Handler | Undefined instruction or illegal state                                                         |  |  |

| starts at memory<br>address 0                                                                                                                       | 0x0000_001C-<br>0x0000_002B     |          |          |                    | Reserved                                                                                       |  |  |

|                                                                                                                                                     | 0x0000_002C                     | 3        | settable | SVC_Handler        | System service call via SWI<br>instruction                                                     |  |  |

| Program Counter pc =                                                                                                                                | 0x0000_0030                     | 4        | settable | DebugMon_Handler   | Debug Monitor                                                                                  |  |  |

| 0x00000004 initially                                                                                                                                | 0x0000_0034                     | -        |          |                    | Reserved                                                                                       |  |  |

|                                                                                                                                                     | 0x0000_0038                     | 5        | settable | PendSV_Handler     | Pendable request for system service                                                            |  |  |

|                                                                                                                                                     | 0x0000_003C                     | 6        | settable | SysTick_Handler    | System tick timer                                                                              |  |  |

|                                                                                                                                                     | · _ · _ · _ · _ · _ · _ · _ · _ |          |          |                    |                                                                                                |  |  |

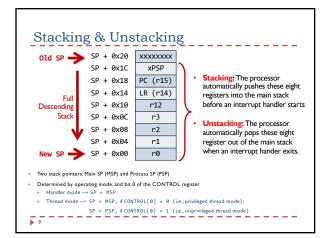

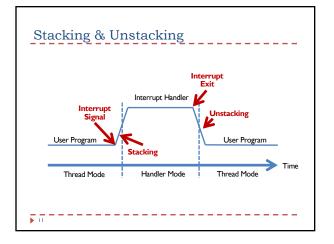

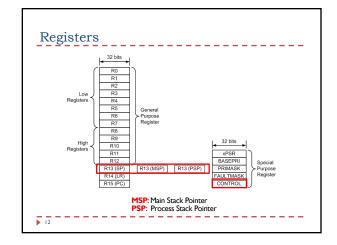

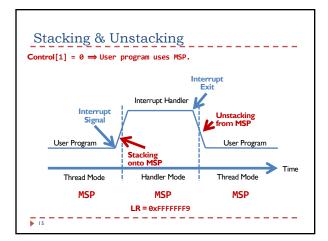

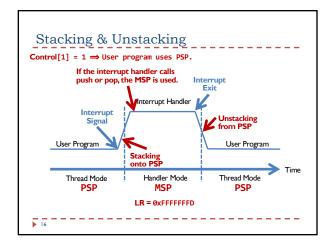

## Processor Mode:

Handler Mode *v*s Thread Mode

- Handler mode and Thread mode

- Handler mode always use MSP (Main Stack Pointer)

- Thread Mode uses either PSP (Process Stack Pointer) or MSP

Control[1] = 0, SP = MSP (default)

- Control[0] = 1, SP = PSP

- > When the processor is reset, the default is the thread mode.

- The processor enters the handler mode when an exception occurs.

13

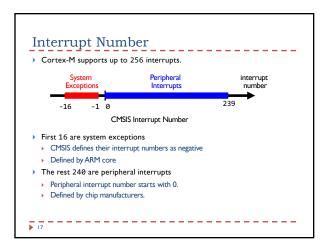

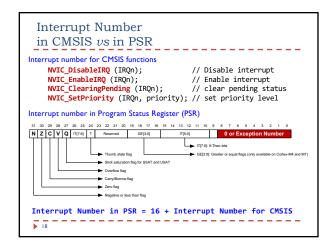

| CMSIS In                                                                                 | torm                                                                             | ıpt Number                                 |                      |     |  |  |  |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------|----------------------|-----|--|--|--|

|                                                                                          |                                                                                  | <u> </u>                                   |                      |     |  |  |  |

| /****** Cortex-M4 Syste                                                                  | m Exceptio                                                                       | ns ************************************    | ***************      | **/ |  |  |  |

| NonMaskableInt_IRQn                                                                      | = -14,                                                                           | /* 2 Cortex-M4 Non Maskable Interrupt      |                      | */  |  |  |  |

| HardFault_IRQn                                                                           | = -13,                                                                           | /* 3 Cortex-M4 Hard Fault Interrupt        |                      |     |  |  |  |

| MemoryManagement_IRQn                                                                    | = -12,                                                                           | /* 4 Cortex-M4 Memory Management Interrupt |                      |     |  |  |  |

| BusFault_IRQn                                                                            | = -11,                                                                           | /* 5 Cortex-M4 Bus Fault Interrupt         | System               | */  |  |  |  |

| UsageFault_IRQn                                                                          | = -10,                                                                           | /* 6 Cortex-M4 Usage Fault Interrupt       | Interrupt Exceptions |     |  |  |  |

| SVCall_IRQn                                                                              | = -5,                                                                            | /* 11 Cortex-M4 SV Call Interrupt          |                      |     |  |  |  |

| DebugMonitor_IRQn                                                                        | = -4,                                                                            | /* 12 Cortex-M4 Debug Monitor Interrupt    |                      |     |  |  |  |

| PendSV_IRQn                                                                              | = -2,                                                                            | /* 14 Cortex-M4 Pend SV Interrupt          |                      |     |  |  |  |

| SysTick_IRQn                                                                             | = -1,                                                                            | /* 15 Cortex-M4 System Tick Interrupt      |                      |     |  |  |  |

| /****** Peripheral Interrupt Numbers ************************************                |                                                                                  |                                            |                      |     |  |  |  |

| WWDG_IRQn                                                                                | = 0,                                                                             | /* Window WatchDog Interrupt               |                      | */  |  |  |  |

| <pre>PVD_PVM_IRQn = 1, /* PVD/PVM1,2,3,4 through EXTI Line detection Interrupts */</pre> |                                                                                  |                                            |                      |     |  |  |  |

| TAMP_STAMP_IRQn                                                                          | TAMP_STAMP_IRQn = 2, /* Tamper and TimeStamp interrupts through the EXTI line */ |                                            |                      |     |  |  |  |

| RTC_WKUP_IRQn                                                                            | = 3,                                                                             | /* RTC Wakeup interrupt through the E      | XTI line             | */  |  |  |  |

| FLASH_IRQn                                                                               | = 4,                                                                             | /* FLASH global Interrupt                  | eripheral            | */  |  |  |  |

| RCC_IRQn                                                                                 | = 5,                                                                             |                                            | iterrupts            | */  |  |  |  |

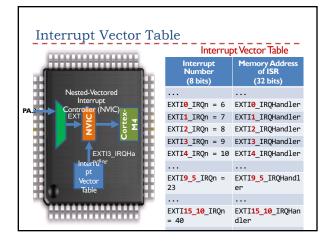

| EXTI0_IRQn                                                                               | = 6,                                                                             | /* EXTI Line0 Interrupt                    | interrupts           |     |  |  |  |

| stm321476xx.h                                                                            |                                                                                  |                                            |                      |     |  |  |  |

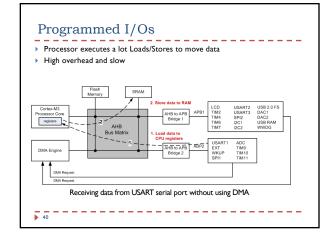

## Basic Concepts of DMA

- Limitations of Interrupt Processing

- CPU involvements

- Good for discrete events with small amount of data

Inefficient for large data transfers

- Needs for High Speed Data Transfer between

- disk and RAM;

- NIC and RAM;

- more

- An analogous example: Program of Study

- Student asks dean for advising and signature → Request

- ▶ Dean directs student to the advisor  $\rightarrow$  address, tasks, and go

- Student talks with the advisor → communication/data transfer

- Advisor signed the program of study after completing advising and send student back o dean for final signature → report completion

1

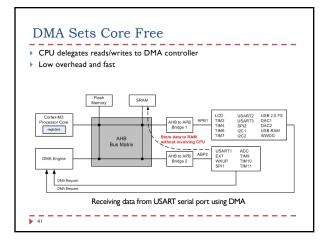

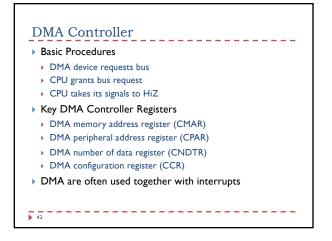

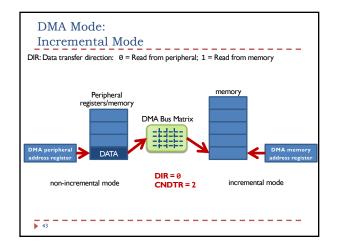

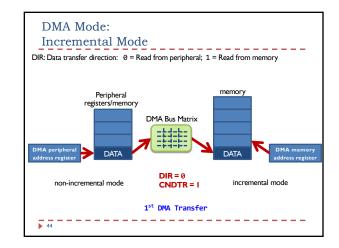

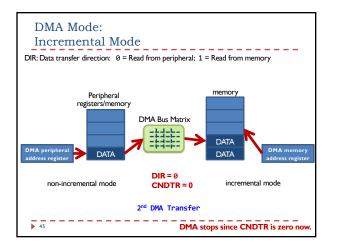

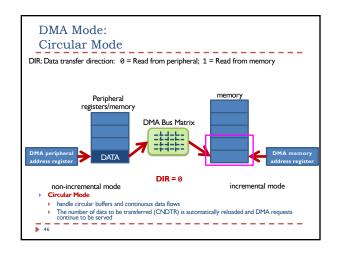

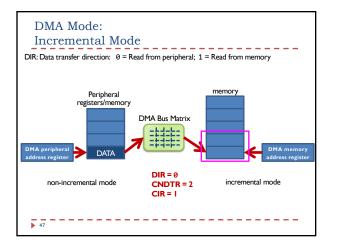

## General Procedure of DMA DMA Request Request from peripheral through hardware Explicit software initiation Channel to channel linking for continual transfer Source/Destination and amount of Data Transfer CPU write registers in DMA controller to define Source address, destination address, and byte count Direct and Continuous Data Transfer Data transfer is done directly between memory and peripheral device without CPU involvement Report Completion When transfer is done, reporting completion through interrupt

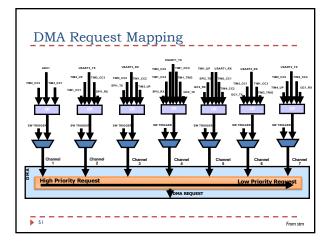

| Direct Memory Access (DMA) DMA releases CPU from moving data between peripherals and memory, or between one peripheral and another peripheral. |         |          |           |                     |           |           |                       |                      |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-----------|---------------------|-----------|-----------|-----------------------|----------------------|

|                                                                                                                                                |         |          | natrix to |                     |           |           |                       |                      |

|                                                                                                                                                |         |          | Channel 2 | Channel 3           | Channel 4 | Channel 5 | Channel 6             | Channel 7            |

|                                                                                                                                                | ADCI    | ADCI     |           |                     |           |           |                       |                      |

|                                                                                                                                                | SPI     |          | SPII_RX   | SPII_TX             |           | SPI2_TX   |                       |                      |

|                                                                                                                                                | USART   |          | USART3_TX | USART3_RX           | USARTI_TX |           |                       |                      |

|                                                                                                                                                | 12C     |          |           |                     | 12C2_TX   | I2C2_RX   | I2CI_TX               | I2CI_RX              |

|                                                                                                                                                | TIM2    | TIM2_CH3 | TIM2_UP   |                     |           | TIM2_CHI  |                       | TIM2_CH2<br>TIM2_CH4 |

|                                                                                                                                                | тімз    |          | тімз_снз  | TIM3_CH4<br>TIM3_UP |           |           | TIM3_CH1<br>TIM3_TRIG |                      |

|                                                                                                                                                | TIM4    | TIM4_CHI |           |                     | TIM4_CH2  | TIM4_CH3  |                       | TIM4_UP              |

|                                                                                                                                                | TIM6    | -        | TIM6_UP   |                     | _         | -         |                       | _                    |

|                                                                                                                                                | DAC_Chl |          | DAC_Ch1   |                     |           |           |                       |                      |

|                                                                                                                                                | TIM7    |          |           | TIM7_UP             |           |           |                       |                      |

|                                                                                                                                                | DAC_CH2 |          |           | DAC_CH2             |           |           |                       |                      |

|                                                                                                                                                | ▶ 39    |          |           |                     |           |           |                       |                      |