#### Computer Organization Laboratory

# Class Notes

#### Instructor: Ken Q. Yang Dept. of ECE, URI

## Section 0

# Course Objectives, Plans, and Lab Tools

#### Course Objectives: What to learn?

- Computer Architecture Concepts

- Instruction Set Architecture

- CPU, Memory, and I/O Organizations

- Interfacing and Communication

- Serial and parallel ports

- UART, DMA, PI/Timer

- Wired and wireless networking

- Applying µProcessor to Design Systems

- Advanced Topics

#### <u>All are based on one specific commercial embedded</u> <u>processor: ARM Processor</u>

UNIVERSITY o

Rhode Island

## Course Plan: How to Learn?

- Regular lectures (twice a week, 1:15 each)

- Covers basic concepts and knowledge

- Explain tools and techniques necessary

- Weekly laboratory experiments (minimum 3 hours/week)

- Assessments:

- 6 Laboratory experiments,

- Each lab accounts for 4% of your grade

- 1 Design project, 20% of your grade

- Design and documentations, 5% of your grade

- Project proposal Presentation (5 minutes), 2%

- Final project presentation (10 minutes), 5%

- demonstration (10 minutes), 8%

- Exams

- 3 exams, each accounts for 20% of your grade

- Two written exams and one lab exam

#### Pope's Inauguration

Then...

When smartphones and tablets *light up the sky, ioad up the clouds.*

Now...

Source : http://www.alternet.org/speakeasy/alyssa-figtora/recording-memories-why-must-we-capture-our-every-moment Rhode Island

#### Era of Internet and Cloud

#### What Happens in an Internet Minute?

\*Source: Intel 2012

### All Boil Down to One Thing

### Computer

A Very Large Fraction: Embedded Computers and Systems

- End user devices

- Variety of appliances

- Network cores

- Consumer Electronics

- More and more

#### Sec. 1. ARM Family Processors

- ARM Cortex<sup>TM</sup>-M Family

- Cortex<sup>TM</sup>-M4 Features

- Kinetis Cortex<sup>TM</sup>-M4 Enhencement

### The Cortex<sup>TM</sup> Processor Family

set top boxes

#### Cortex<sup>™</sup>-A

mobile applications

Cortex<sup>™</sup>-R

disk drives

: 0

digital cameras

mobile baseband

Cortex<sup>™</sup>-M

motors

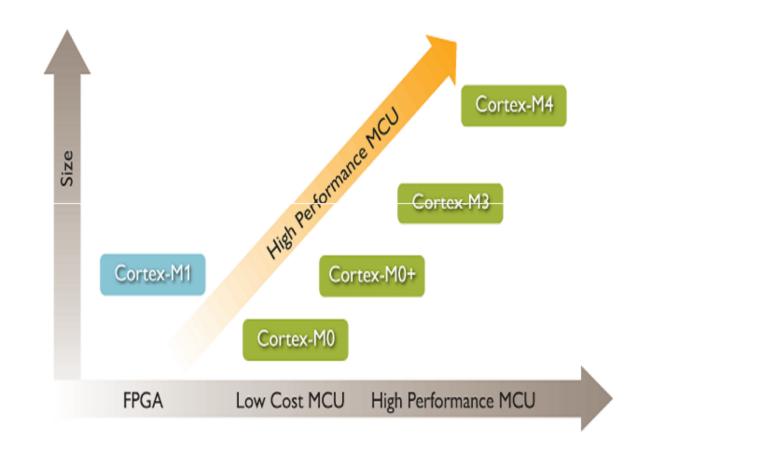

#### Range of Cortex-M

# Outline

- ARM Cortex<sup>TM</sup>-M Family

- Cortex<sup>TM</sup>-M4 Features

- Kinetis Cortex<sup>TM</sup>-M4 Enhencement

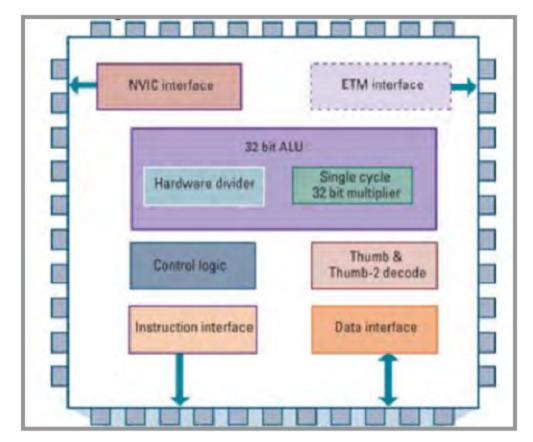

### What is Cortex<sup>TM</sup>-M

- Harvard Architecture

- 3 stage pipeline

- Single cycle multiply

- Hardware Divide

- Thumb-2 Instruction Set

- Vectored Interrupt Controller

UNIVERSITY of Rhode Island

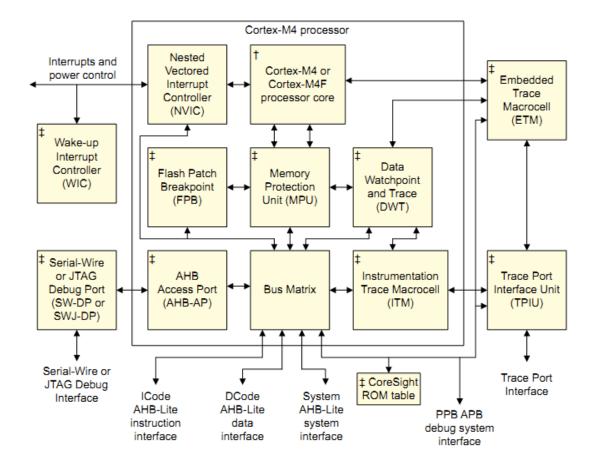

#### CORTEX M-4

† For the Cortex-M4F processor, the core includes a Floating Point Unit (FPU)

‡ Optional component

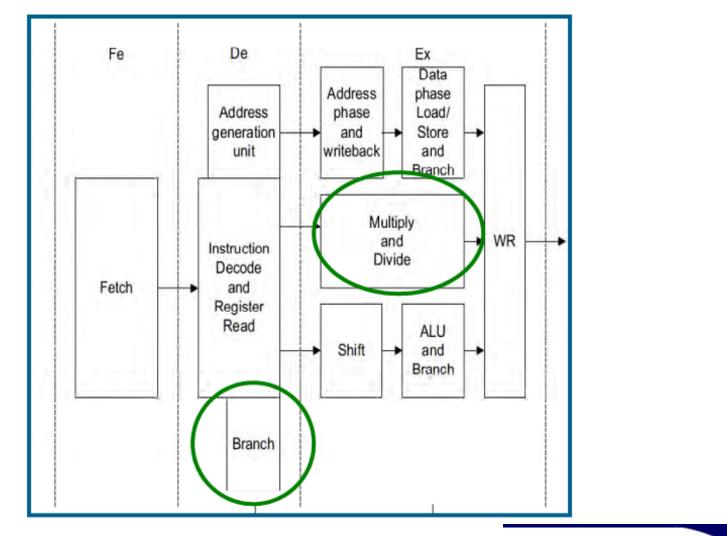

#### Cortex<sup>TM</sup>-M Pipeline

#### ARM® Instruction Set – Some History

- ARM Instruction Set

- Original 32-bit Instruction Set

- Thumb Instruction Set

- 16-bit Instruction Set

- Thumb-2 Instruction Set

- Mixed 16/32 bit Instruction Set

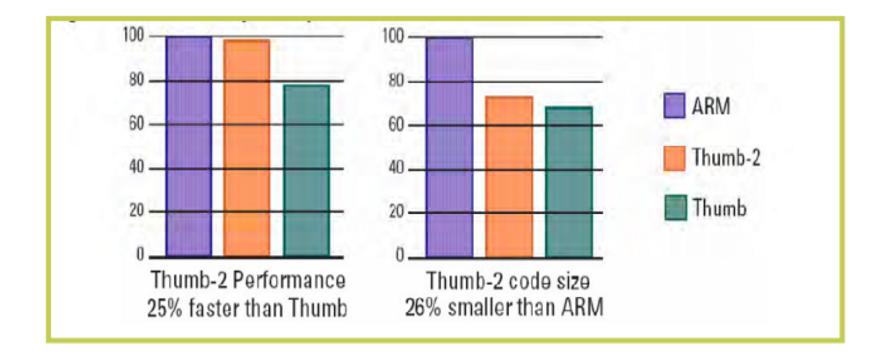

#### Effects of the Thumb-2 ISA

# Register Sets 1

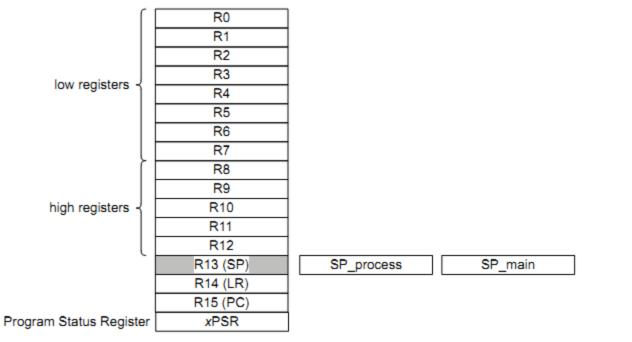

The processor has the following 32-bit registers:

- 13 general-purpose registers, R0-R12

- Stack Pointer (SP), R13 alias of banked registers, P\_process and SP\_main

- Link Register (LR), R14

- Program Counter (PC), R15

- Special-purpose Program Status Registers, (xPSR).

# Register Sets 2

#### Low registers

Registers R0-R7 are accessible by all instructions that specify a general-purpose register.

#### **High registers**

Registers R8-R12 are accessible by all 32-bit instructions that specify a general-purpose register.

Registers R8-R12 are not accessible by any 16-bit instructions.

#### Registers R13, R14, and R15 have the following special functions:

#### Stack pointer

Register R13 is used as the Stack Pointer (SP). Because the SP ignores writes to bits [1:0], it is auto aligned to a word, four-byte boundary.

Handler mode always uses SP\_main, but you can configure Thread mode to use either SP\_main or SP\_process.

#### Link register

Register R14 is the subroutine Link Register (LR).

The LR receives the return address from PC when a Branch and Link (BL) or Branch and Link with Exchange (BLX) instruction is executed.

The LR is also used for exception return.

At all other times, you can treat R14 as a general-purpose register.

#### **Program counter**

Register R15 is the Program Counter (PC).

Bit [0] is always 0, so instructions are always aligned to word or half word boundaries.

#### Programmers Model 1

|       | 31 | 30 | 29 | 28 | 27 26 25  | 24 23 | 20 | 19   | 16   | 15           | 10 9        | 8        | 0             |

|-------|----|----|----|----|-----------|-------|----|------|------|--------------|-------------|----------|---------------|

| APSR  | N  | z  | с  | v  | Q         |       |    | GE[3 | :0]† |              |             |          |               |

| IPSR  |    |    |    |    |           |       |    |      |      |              | Second Sec. | 0 or Exc | eption Number |

| EPSR  |    |    | 7  | 1  | ICI/IT    | т     |    |      | 1    | ICI/IT       |             |          |               |

| Reser |    |    |    |    | P Extensi | on    |    |      | F    | Reserved (se | e text)     |          | 6             |

- APSR Application process status register

- **IPSR** Interrupt process status register

- **EPSR** Execution process status register

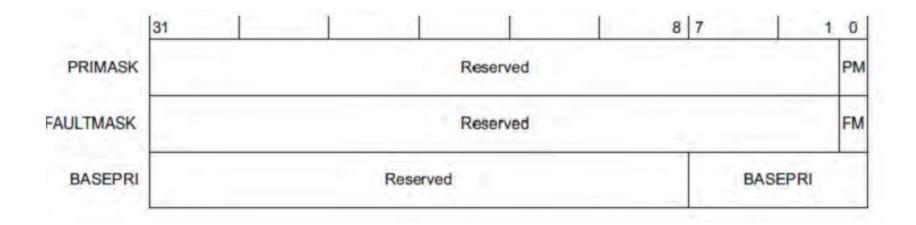

### Programmers Model 2

PRIMASK – Disable all interrupt except NMI and hard fault

FAULTMASK – Disable all interrupt except NMI

BASEPRI – Disable all interrupt of specific priority and lower

#### Programmers Model 3

#### **Control Register**

nPRIV, bit[0] Defines the execution privilege in Thread mode:

0Thread mode has privileged access1Thread mode has unprivileged access.

-----Note -------

In Handler mode, execution is always privileged.

SPSEL, bit[1] Defines the stack to be used:

0

- Use SP\_main as the current stack

- In Thread mode, use SP\_process as the current stack.

In Handler mode, this value is reserved.

FPCA, bit[2], if the processor includes the FP extension

Defines whether the FP extension is active in the current context:

- FP extension not active.

- FP extension is active.