## Concepts of Serial Communication

- · Limitations of Parallel Bus

- Clock skew becomes a serious issue for high speed and long distance

- Cost of wire, fewer wires cost less and occupies less space

- Cross talk between multiple conductors, affecting signal quality

- · Serial Communication

- Sending data a bit at a time, sequentially, over a communication channel

- Un-clocked, no clock skew problem

- Fewer wires → low cost, more space for better isolation from surroundings

- · Simplex, half-duplex, and full-duplex

- Simplex: data can be transferred in only one direction

- Half-duplex: data can be transferred in two directions, but one at a time

- Full-duplex: data can be transferred in two directions concurrently

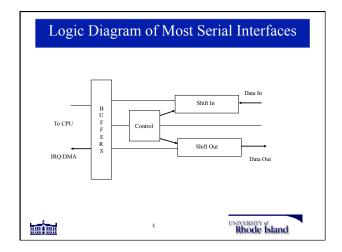

#### General Procedure and Logic of Serial Communication

- Special signal marks

- Start bit and stop bit that mark the begin and end of one comm

- · Parity bit

- Error checking and correction

- Even parity, odd parity, CRC, Hamming code, etc.

- Baud rate

- Specifies how fast bit sequence is transmitted

- · Buffering for transmitter and receiver

1

### **UART** Instantiations on Kinetis

| UART<br>Instance | ISO-7816<br>Supported? | FIFOs                                         | Module<br>Clock                            | Maximum<br>Baud Rate |

|------------------|------------------------|-----------------------------------------------|--------------------------------------------|----------------------|

| UART0            | Yes                    | 8 entry TxFIFO<br>8 entry RxFIFO              | Core Clock<br>(Max freq =<br>100 MHz)      | 6.25 Mbits/sec       |

| UART1            | No                     | 8 entry TxFIFO<br>8 entry RxFIFO              | Core Clock<br>(Max freq =<br>100 MHz)      | 6.25 Mbits/sec       |

| UART2-UART5      | No                     | No FIFOs<br>(double<br>buffered<br>operation) | Peripheral<br>Clock (Max<br>freq = 50 MHz) | 3.13 Mbits/sec       |

| OTH       | 1   | Dela                                                | niled Signal Desci                                                                                                                                                                       | ptions               |

|-----------|-----|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Signal    | 1/0 | Description                                         |                                                                                                                                                                                          |                      |

| CTS       |     | Clear to send. Is                                   | ndicates whether the UART can start transmitting data when flow control is<br>enabled.                                                                                                   |                      |

|           |     | State meaning                                       | Asserted—Data transmission can start.                                                                                                                                                    |                      |

|           |     |                                                     | Negated—Data transmission cannot start.                                                                                                                                                  |                      |

|           |     | Timing                                              | Assertion—When transmitting device's RTS asserts.                                                                                                                                        |                      |

|           |     |                                                     | Negation—When transmitting device's RTS deasserts.                                                                                                                                       |                      |

| RTS       | 0   | Request to se<br>receive data. V                    | ond. When driven by the receiver, indicates whether the UART is ready to<br>When driven by the transmitter, can enable an external transceiver during<br>transmission.                   |                      |

|           |     | State                                               | Asserted-When driven by the receiver, ready to receive data. When                                                                                                                        | 1                    |

|           |     | Meaning                                             | driven by the transmitter, enable the external transmitter.                                                                                                                              |                      |

|           |     |                                                     | Negated—When driven by the receiver, not ready to receive data. When driven by the transmitter, disable the external transmitter.                                                        |                      |

|           |     | Timing                                              | Assertion—Can occur at any time; can assert asynchronously to the other input signals.                                                                                                   |                      |

|           |     |                                                     | Negation—Can occur at any time; can deassert asynchronously to the<br>other input signals.                                                                                               |                      |

| RXD       | - 1 |                                                     | Receive data. Serial data input to receiver.                                                                                                                                             |                      |

|           |     | State meaning                                       | Whether RXD is interpreted as a 1 or 0 depends on the bit encoding method along with other configuration settings.                                                                       |                      |

|           |     | Timing                                              | Sampled at a frequency determined by the module clock divided by the<br>baud rate.                                                                                                       |                      |

| TXD       | 0   | Transmit data. Serial data output from transmitter. |                                                                                                                                                                                          |                      |

|           |     | State meaning                                       | Whether TXD is interpreted as a 1 or 0 depends on the bit encoding method along with other configuration settings.                                                                       |                      |

|           |     | Timing                                              | Driven at the beginning or within a bit time according to the bit encoding method along with other configuration settings. Otherwise, transmissions are independent of reception timing. |                      |

| Collision | 1   | Collision                                           | Detect. Indicates if a collision is detected during Data Transmission.                                                                                                                   | 1                    |

|           |     | State                                               | Asserted-Indicates a collision detection. UARTxCPW determines the                                                                                                                        | 1                    |

|           |     | Meaning                                             | length of this pulse for valid collision detection.  Negated—No collision detected.                                                                                                      |                      |

|           | 1   | Timing                                              | Asserts asynchronously to other input signals.                                                                                                                                           | RSITY of node Island |

## **UART Modes of Operation**

- ▶UART module supports three main operating modes:

- · UART mode

- · Supported on all 6 UARTs

- · IrDA mode

- · Support on all 6 UARTs

- · ISO-7816 mode

- · Only supported on UART0

9

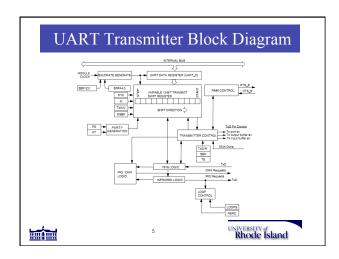

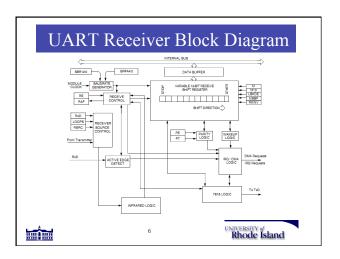

### **UART Mode Features**

- · Full-duplex serial communication

- Standard mark/space non-return-to-zero (NRZ) format

- 13-bit baud rate selection with /32 fractional divide, based on module clock frequency

- Programmable data formats

- 8- or 9-bit data formats including 9-bit with parity

- Programmable transmitter output and receiver input polarity

Ability to select MSB or LSB to be first bit on wire

- 8 entry Rx and Tx FIFOs available on UART0 and UART1

- Hardware flow control support for request to send (RTS) and clear to send (CTS) signals

- Address match feature in receiver to reduce address mark wakeup ISR overhead

- · Hardware parity generation and checking

- Interfaced to the on-chip DMA

- nterfaced to the on-chip DMA

DMA Rx and Tx requests from the UART can be used to move data without processor intervention

10

#### IrDA Mode Features

- · Selectable IrDA 1.4 return-to-zero-inverted (RZI) format

- · Programmable narrow pulse transmission and detection

- Support IrDA data rates between 2.4 kbits/s and 115.2 kbits/s

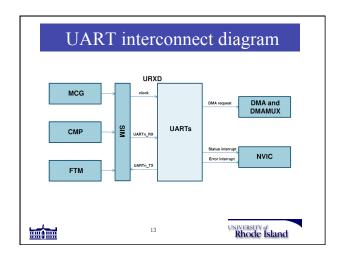

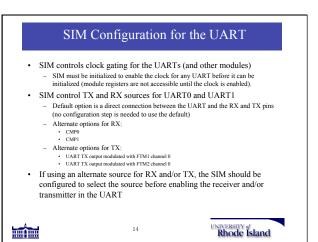

- Several options for changing RX and TX sources for UART0 and UART1 are controlled by the SIM:

- UARTn\_RX input from the pin or from CMP0 or CMP1

- UARTn\_TX output directly from UART or modulated with FTM outputs

- These options can be used in any UART mode, but are most useful for IrDA applications

- ► NOTE: Although all UARTs include IrDA features only UART0 and UART1 have the alternate options for the TX and RX sources controlled by the SIM

UNIVERSITY of Rhode Island

#### ISO-7816 Mode Features

- Support for ISO-7816 protocol for interfacing with SIM and smartcards

- Support of T=0 and T=1 protocols

- Automatic retransmission of NACK'd packets with programmable retry threshold

- Support for 11 and 12 ETU transfers

- Detection of initial packet and automated transfer parameter programming

- Interrupt-driven operation with seven ISO-7816 specific interrupts

- Wait Time Violated

- Character Wait Time Violated

- Block Wait Time Violated

Initial Character Detected

- Transmit Error Threshold Exceeded

- Receive Error Threshold Exceeded

Guard Time Violated

12

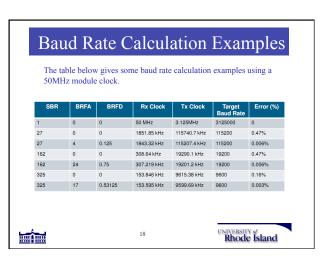

# **Baud Rate Calculation** • The UART has a 13-bit integer divider and a 5-bit fractional fine adjust counter that are used to generate the UART baud rate. UART baud rate = UART module clock/ (16 \* (SBR[12:0] + BRFD)) • Where BRFD = the BRFA[4:0] field divided by 32 Rhode Island

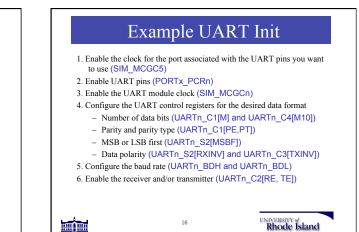

### Polling, Interrupt, or DMA configuration

- The UART can be configured to handle data flow by polling status flags, generating interrupts, or using the DMA.

- Polling is the most CPU intensive, but might make the most sense when

- handling small messages.

The UART status interrupt can be used to decrease CPU loading. Status interrupt conditions are:

- Interrupt conditions are:

Transmit data empty

Transmit complete

Idle line (primarily used for multi-drop applications)

Receive data full

LIN break detect

RxD pin active edge (main use is as a CPU wakeup)

Initial character detect (used for ISO-7816 mode only)

- The DMA can be used to automatically move receive and/or transmit data to reduce CPU loading even more. DMA requests can be generated on:

Transmit data empty

Receive data full

19